脉冲信号

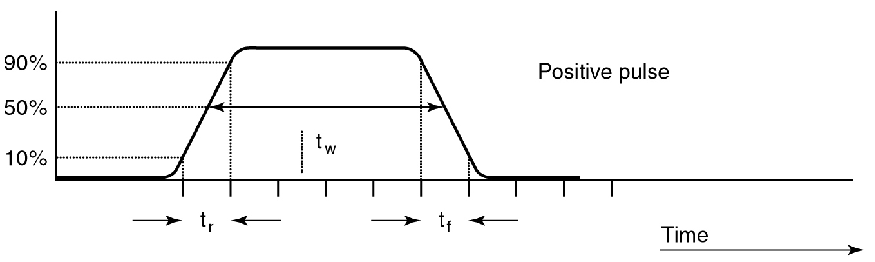

在活动状态和非活动状态之间切换的信号称为脉冲波形。

正脉冲具有高电平有效电平。

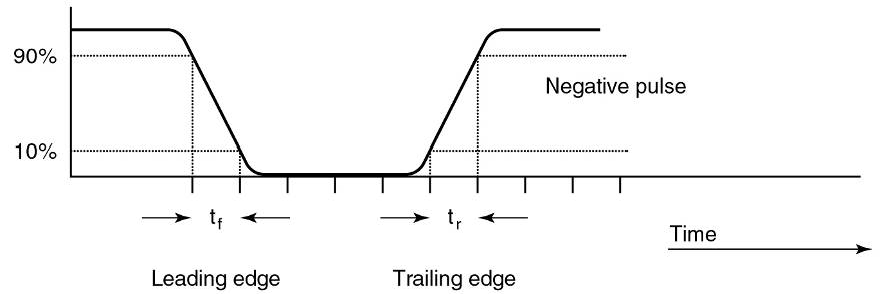

负脉冲具有低电平有效。

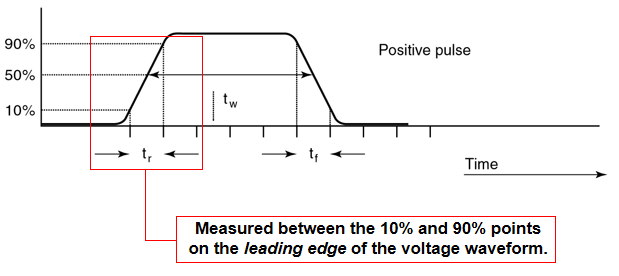

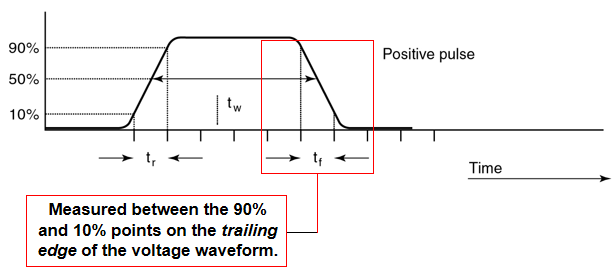

在实际电路中,脉冲波形从一个电平变为另一电平需要时间。

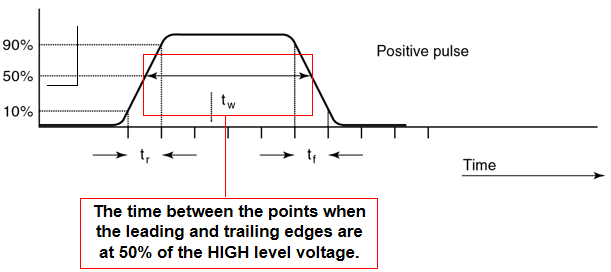

正脉冲从低电平到高电平的过渡称为上升时间(tr)。

在实际电路中,脉冲波形从一个电平变为另一电平需要时间。

在正脉冲上从高电平过渡到低电平的过程称为下降时间(tf)。

在实际电路中,脉冲波形从一个电平变为另一电平需要时间。

脉冲也具有持续时间-宽度-(tw)。

时钟信号与同步触发器

数字系统可工作在同步或异步两种工作方式中。在异步系统中,逻辑电路输出状态可以在一个或多个输入改变的任意时刻变化。一般来说,异步系统比同步系统更加难以设计和调试

- 异步系统-输出可以随时更改输入的状态。

- 同步系统-输出只能在时钟周期的特定时间更改状态。

在同步系统中,所有的输出只能在特定时刻改变状态,而这个时刻由“时钟信号”决定,时钟信号通常是一个矩形脉冲序列或一个方波,如图所示,时钟信号被分配到系统各个部分,系统中大多数的输出只能在时钟跳变时改变状态。

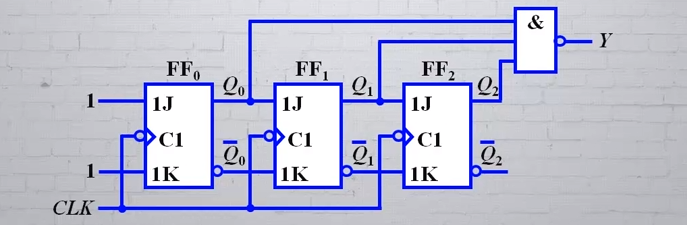

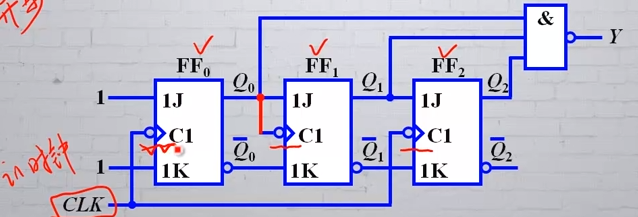

这就是一个同步时序

观察可以发现,这三个触发器都有一个共用一个外部输入时钟信号,并且C1都是由一个小圆圈一个三角形组成的,这就是同步时序

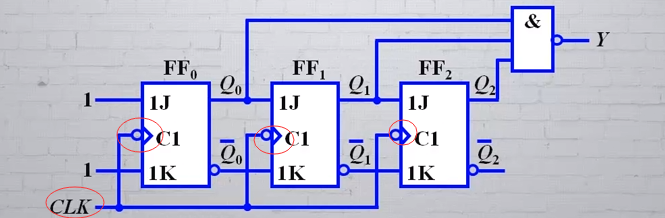

这就是一个异步时序

观察可以三个触发器仍然共用一个外部输入时钟信号。但是第三个C1和前面两个不一样,这个时候三个触发器工作时刻不是统一的。这就是异步时序

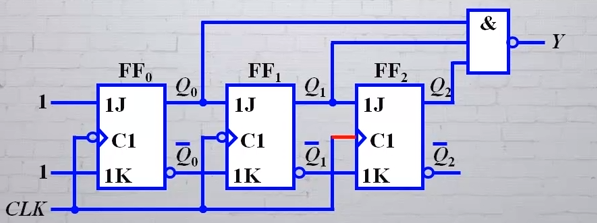

另外一种异步时序

三个C1都是一样的,但是我们发现中间的外部时钟不一样。这也是异步时序的一种

跳变(也称为边沿)

- 当时钟由0改变到1时,称为上升沿(PGT)跳变

- 当时钟由1改变到0时,称为下降沿(NGT)跳变

时钟信号的同步动作是利用同步触发器来完成的。同步触发器被设计成在某个时刻的跳变时刻改变其状态。

同步触发器

同步触发器的类型很多,下面是一些它们共同的主要概念

- 同步触发器有一个时钟输入端,标以CLK、CK或CP。我们常用CLK,如图所示。多数同步触发器的时钟驶入是边沿触发的。这意味着它在信号跳变时有效,在图中由CLK端的小三角表示。这与锁存器不同,锁存器是电平触发的。

图片左边的触发器在CLK端标有一个小三角,用以指出CLK输入只在上升沿时有效;输入脉冲的其他部分不会对CLK输入端产生影响。

图片右边所示的触发器符号中,CLK输入端有一个小圆圈和小三角。这是指CLK输入只在下降沿时有效;输入脉冲的其他部分不会对CLK输入端有影响。 - 同步触发器还有一个或多个控制输入端,它们可以有不同的名称,这取决于它们的作用。控制输入端只有当时钟跳变发生时才会对Q端输出产生影响,换言之,它们的影响与CLK端的信号是同步的,因此,称这些控制输入端为同步控制输入

图片左边的控制输入只有当时钟信号上升沿到来时才会对Q端产生影响,同样图片右边的控制输入只有当时钟信号下降沿到来时才有效 - 总之我们可以说控制输入为触发器输出的改变做好了准备,而CLK输入的有效跳变真正触发了触发器输出端状态的改变。控制输入决定“如何变”(即输出将要变为什么状态)而CLK输入决定“何时变”