HDL(AHDL和VHDL) 硬件描述语言

前面的内容无论是上划线,原理图符号,还是表格,作为计算机输入时都存在一定难度。

有一种更为先进的描述方法,它们更适合在数字领域用来描述实现特定功能的逻辑电路

这种方法称为 硬件描述语言(HDL)

其中Altera公司研发的硬件描述语言AHDL和超高速集成电路硬件描述语言VHDL

用PLD实现逻辑电路

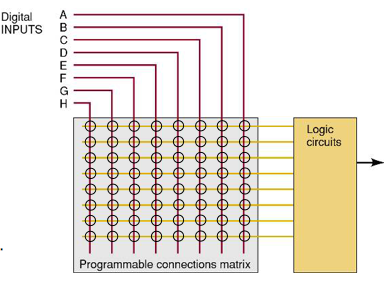

PLD:可编程逻辑器件;

使用PLD的话设计人员自行编程而把一个数字系统“集成”在一片PLD上,而不必去请芯片制造厂商设计和制作专用的集成电路芯片了。

如今许多数字电路都是用可编程器件(PLD)实现的,这类器件与运行指令程序的微型计算机和微控制器不同,它们是由电子学方法构成的,其内部电路通过导线相互连接从而形成逻辑电路。

这种可编程的连线可认为是几千个连接(1)或不连接(0)的节点

上图是一小规模的可编程连接矩阵,行和列之间的每一个交叉点为可编程的连接

在20世纪70年代的时候,人们就是手工在每一个网格上放置1和0来重构这些器件,可想是多么麻烦

硬件描述语言的作用是为设计者描述电路的工作过程提供一种简洁且方便的方法,且这种描述形式使PC机容易处理和存储。

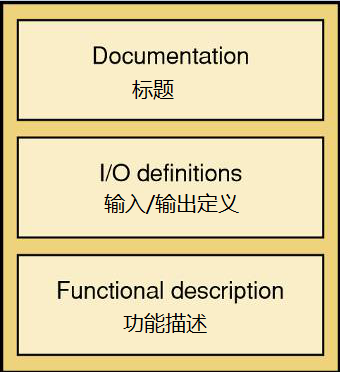

HDL的格式和语法

任何一种语言都具有其独一无二的特点和独特的语法,任一硬件电路描述的基本格式包括两个重要的要素:

- 输入、输出的定义(即输入、输出说明)

- 对输出如何响应输入的定义(工作原理)

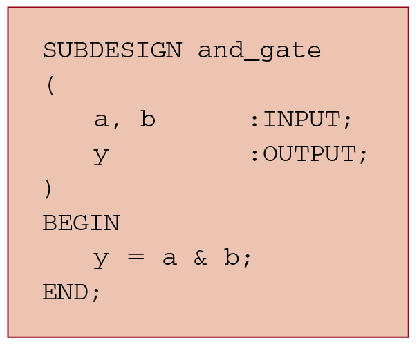

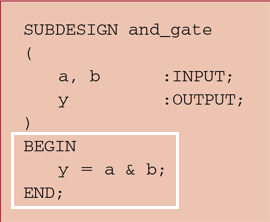

采用AHDL的布尔表达式描述

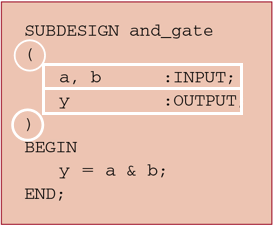

关键字SUBDESIGN给电路模块命名,在此图中电路模块命名为and_gate.tdf

注意关键字SUBDESIGN大写,这不是强制性的,但是采用大写使程序更容易阅读

SUBDESIGN程序段定义了逻辑电路程序模块的输入/输出,有时必须包括我们所描述的电路,这一点类同于框图应包含设计的各个组成部分。

本程序块所用到的输入变量中,各个变量之间用逗号分开,紧随之后的是变量类型说明:INPUT;

(在AHDL中,除标明变量是多位的外,一般假定是单个位数据类型)

输出位用模式:OUTPUT;

关键字BEGIN和END之间为逻辑功能描述段,其中包含了AHDL中描述电路工作原理的一组语句。本例中用了一个布尔代数方程式来描述

它表示把a和b进行与运算所产生的逻辑电平赋值给输出y

布尔代数方程式称为并行赋值语句,BEGIN和END之间的任何语句其求值过程是并发的,即与各个语句出现的先后顺序无关

基本布尔运算符为:

& 与

# 或

! 非

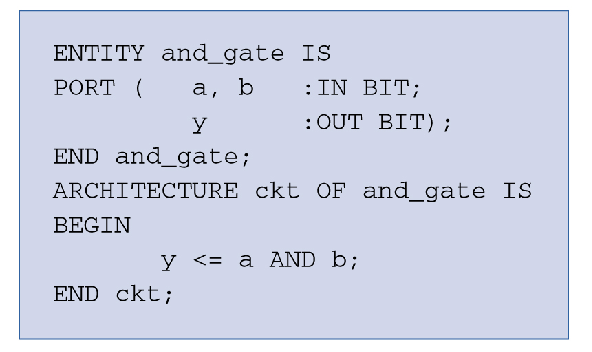

$ 异或采用VHDL的布尔表达式描述

由关键字ENTITY给电路程序块命名,此处程序块名称为and_gate

关键字ENTITY大写,但and_gate小写,不是强制性的,但是为了便于阅读

关键字ENTITY可认为是描述程序块的说明

在VHDL中,关键字PORT告诉编程程序我们已给本电路程序块定义输入输出

输出名称之间用逗号分开

后面是冒号和输入信号类型及模式的描述 :IN BIT;

在VHDL中,BIT告诉编译程序,表中的每一个输入变量都是单个位变量。

以END and_gate行结束ENTITY说明

用ARCHITECTURE说明描述程序块内的每一个操作

设计者会给ENTITY程序块内部结构体的描述命名(可以看到在本例中名称为ckt)

每个ENTITY至少包含一个ARCHITECTURE,此说明中OF和IS是关键字

结构体的描述应该在关键字BEGIN和END之间,END之后应该是前面指定的结构体名称(本例中为ckt)

BEGIN和END之间是对程序块所执行的操作的描述,本例中 硬件电路的操作由一个简单的布尔代数方程来描述

它表明a与b的结果赋值给(<=)输出y

这叫做并行赋值语句,它表明BEGIN和END之间的所有语句其求值过程是并发的,即与各个语句出现的先后顺序无关

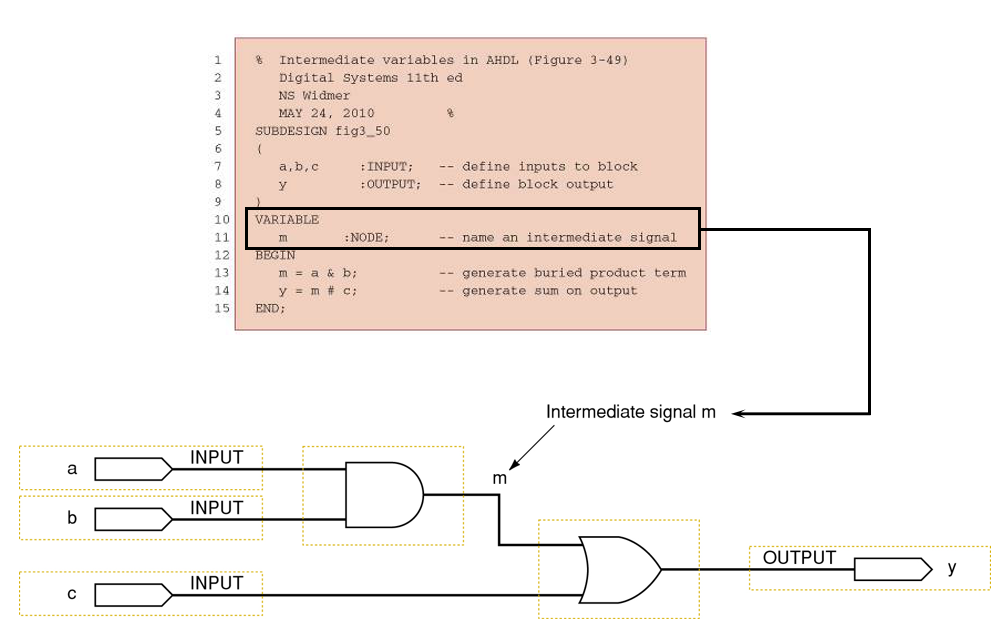

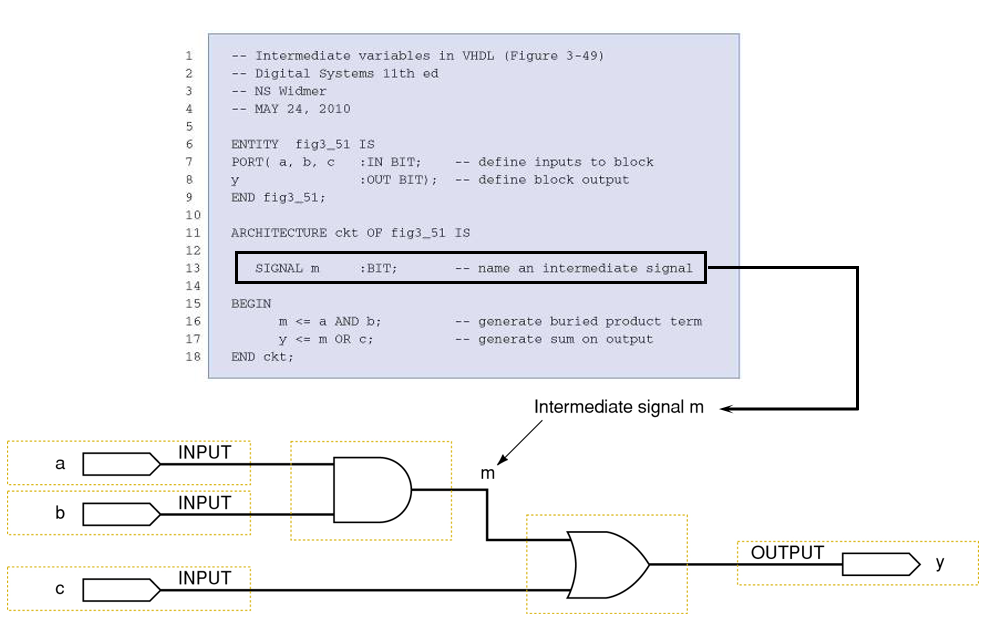

中间信号 AHDL的内部节点 VHDL中的局部信号

在许多设计中,经常需要定义电路模块内部的信号点。电路内部的这些信号点既不是模块的输入也不是输出,但作为参考点是十分有用的,它也可以是在模块内部需要连接到多处的一个信号

在模拟和数字电路的原理图中,它们也叫做测试点或节点,在HDL中,称它们为内部节点或局部信号

在上图简单电路中,即用到了名称为m的中间信号

在HDL这些节点(信号)与输入输出分开定义,即节点在程序块中的逻辑功能描述段定义

在这个程序里,请注意程序开头的信息,这些信息主要是用于文件的说明,它对于记录设计资料是相当重要的。这部分内容至少应包含使用该程序块的目的、程序的作者、设计日期等,此段信息通常称为标题段。

上述的标题段,其实是多行注释,在AHDL中,多行注释被包含在两个%字符之间

在程序的中间部分有许多使用--两个短划线的注释,短划线后面直到本行结束前都是注释

AHDL

在AHDL中,局部信号在VARIABLE段说明,位置介于SUBDESIGN段与逻辑功能描述段之间

在关键字VARIABLE之后,第11行定义了中间变量m,关键字NODE指明变量的特性,注意用冒号分开

在第13行的硬件描述中,给中间变量赋值,然后第14行语句中m用在了给y赋值的语句中(赋值的语句是并发的,先后顺序无所谓)

VHDL

在第13行的关键字SIGNAL之后,定义了m这个中间信号。关键字BIT指明了信号的类型,注意在信号名称与类型说明之间用冒号分开。

在第16行的硬件描述中,给中间信号赋值,第17行在给y赋值的语句中用到了m(赋值的语句是并发的,先后顺序无所谓)