确认有效电平

当一个逻辑信号处于其有效状态时,可以说成是被确认。例如当我们说输入信号A0被确认时,也就是说,它处于低电平有效状态。

当一个逻辑信号不是有效状态时,可以说成是未被确认。

因此如果说DRIVE未被确认,也就是说,它处于无效状态(低电平)

确认(asserted) = 有效(active)

未确认(unasserted) = 无效(inactive)

标记低电平有效逻辑信号

用上划线标记低电平有效信号

没有上划线表示信号是高电平有效

标记双有效状态信号

一个输出信号经常会有两个有效状态,也就是说

它有一个重要功能在高电平有效状态

及另一个重要功能在低电平有效状态

一个常见的例子是 读/写 信号

当这个信号是高电平时,完成读操作(RD)

当它是低电平时,完成写操作(WR)

传播延迟

传播延迟是系统收到输入后产生输出所需的时间。

逻辑电路的速度与传播延迟有关。

实际的数字电路可以测量传播的延迟时间

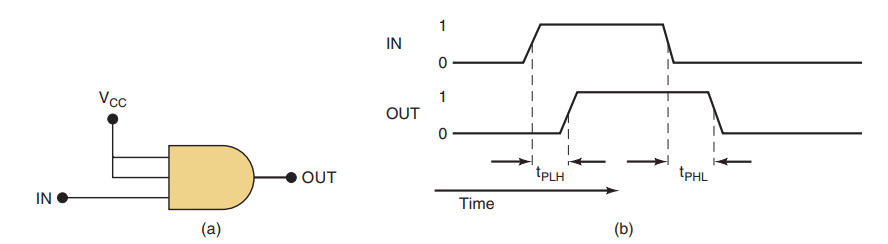

如图(a)所示,与门用作确实存在传播延迟并且可以对其进行测量的示例。

当IN信号变为高电平时,将导致OUT信号在不久后变为高电平。同样,当IN信号变为LOW时,它会使OUT信号在短时间内变为LOW

使输出变为高电平所需的时间不一定与使输出变为低电平所需的时间相同。这些延迟时间称为

tPLH(从低到高的时间传播)

tPHL(从高到低的时间传播)

逻辑电路的速度与传播延迟的特性有关。无论选择哪种器件来实现逻辑电路,都将具有一个数据手册,该手册说明传播延迟的值。该信息用于确保电路可以针对应用足够快地运行。