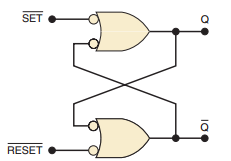

最基本的触发器电路可以由两个与非门或两个或非门构成,由与非门构成的称为与非门锁存器,或简称为锁存器

如图所示,两个与非门交叉连接,与非门1的输出和与非门2的一个输入相连。与非门1的输入和与非门2的输出相连

门的输出端,标着Q和Q非端的是锁存器的输出端

锁存器有两个输入端,置位输入使Q为1状态,清零输入使Q为0状态

置位和清零端通常处于高电平状态,要想改变锁存器的输出,其中一个输入端就得输入一个低电平脉冲。

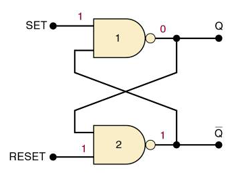

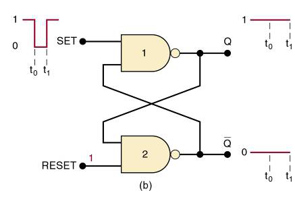

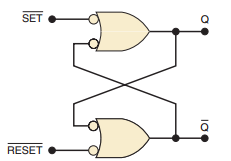

我们从SET=RESET=1时的两种可能的输出状态:

第一种:如上图所示,Q=0,Q非=1

因为Q=0,则门2的输入是0和1,使Q非=1 。从Q非得到的1使门1的两个输入端都为1,使Q=0 。从门1输出的低电平使门2的输出为高电平,而门2输出的高电平也使门1的输出维持在低电平

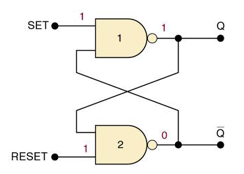

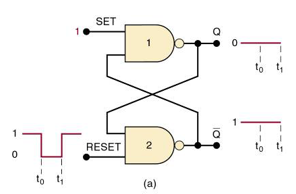

第二种:如下图所示,设Q=1,Q非=0

门1的高电平使门2输出低电平,门2的低电平使门1的输出保持高电平

这样当SET=RESET=1时,就有两种可能的输出状态

输出的状态取决于输入端的预置状态

锁存器(触发器)置位

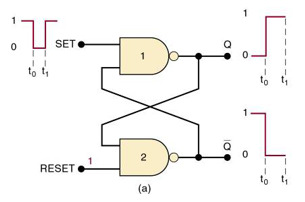

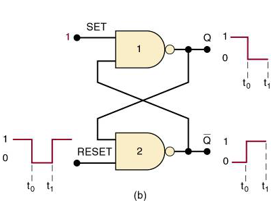

当RESET端维持高电平时,给SET端一个低电平脉冲时,下图是在脉冲到来之前,当原始状态为Q=0时系统的变化情况

t0时刻,SET端到来一个低电平脉冲,Q变为高电平,并使Q非变为低电平,使门1两个输入端都为低电平。这样,当SET端在t1时刻回到1时,门1的输出保持高电平,门2的输出保持低电平

下图是当原始状态为Q=1,Q非=0时,置位脉冲的作用。

因为Q非=0使门1输出为高电平,SET端的脉冲不起作用。当SET端恢复成高电平时,锁存器的输出依然是Q=1,Q非=0

我们可以总结为:置位端(SET端)的低电平脉冲总是使锁存器最终处于Q=1的状态,这称为锁存器或触发器置位

锁存器(触发器)清零

当SET端保持高电平时,清零输入低电平脉冲的情况,下图是当原始状态为Q=0和Q非=1时,清零输入低电平脉冲时的情形。

因为Q=0使门2的输出保持高电平,清零端的低电平脉冲不起作用。当清零端恢复高电平时,锁存器输出任为Q=0和Q非=1

下图是当原始态为Q=1时,清零脉冲作用的情形。

t0时刻,清零端输入低电平脉冲,Q非变为高电平,这个高电平使Q变为低电平,结果门2的两个输入都是低电平。当清零端在t1时刻恢复高电平时,门2的输出仍保持高电平,致使门1输出仍保持低电平

总结为:清零端的低电平脉冲总是使锁存器处于Q=0的状态,这称为锁存器的清零或复位。

同时置位和清零

最后一种情况是置位端和清零端同时输入低电平脉冲,这将使两个与非门的输出都为1,即Q=Q非=1

显然,这是一种不允许的情况,因为两个输出端的状态应该相反;而且当置位端和清零端恢复到高电平时,输出的结果将取决于哪一个输入端先恢复到高电平。同时回到“1”态将使电路产生不确定的结果。因此SET=RESET=0在与非门锁存器中通常不用,属于禁止输入状态。

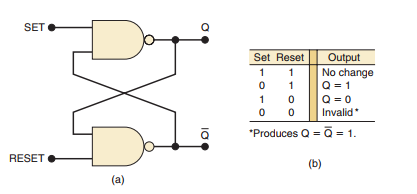

与非门锁存器总结

与非门锁存器的功能可归纳为一个真值表

- 当SET=RESET=1,是输入端的常态,对输出的状态没有影响。Q和Q非端仍将保持这个输入状态到来之前的状态

- SET=0,RESET=1总使输出端Q=1,SET端回到高电平后,输出仍会保持Q=1,这称为锁存器置位

- SET=1,RESET=9,使Q=0,当RESET端恢复高电平后,输出依然保持Q=0,这称为锁存器清零或复位

- SET=RESET=0,使锁存器同时置位和清零,得到Q=Q非=1,如果输入端同时回到1,会导致输出结果不定,它属于禁止输入状态

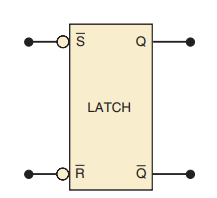

用替代符号表示与非门锁存器

SET和RESET两个输入端是低电平有效,当SET为低电平时,使Q=1,当RESET为低电平时,使Q=0

因此,与非门锁存器中的每个与非门常用替代形式表示

输入端的小圆圈与符号上的小横线一样,都表示这些输入端低电平有效

下图是常用的简化逻辑符号

S和R分别代表SET端和RESET端,小圆圈表示这两个输入低电平有效

专业术语

触发器或锁存器的清零又称为复位,在数字领域,这两个词可以互换使用。清零输入也可称为复位输入,置位-清零锁存器也可称为置位-复位锁存器

例

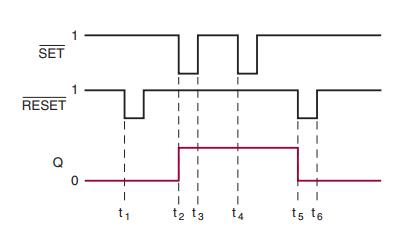

上图的锁存器的输入波形如下图所示,设初始状态是Q=0,画出输出端Q的波形